# Low EMI 1A Transformer Driver for Isolated Power Supplies

## **Features**

- Push-pull driver for transformers

- Operates with 2.25-V to 5.5-V supply

- High output drive: 1A at 5V supply

- Low R<sub>ON</sub> 0.25Ω at 4.5V

- Spread spectrum clocking (SSC)

- Ultra-low EMI

- Precision internal oscillator options:

- > 160kHz (COS6505A)

- > 420 kHz (COS6505B/C)

- Synchronization of multiple devices with external clock input

- Slew-rate control

- 1.7A Current-limit

- Low shutdown current: <1 µA</p>

- Thermal shutdown protection

- Wide temperature range: –45°C to 125°C

- Small package: SOT23-6

# **Applications**

- Isolated Interface Power Supply for CAN, RS-485, RS422, RS-232, SPI, I2C

- Low-Power LAN

- Isolated USB Supplies

- Industrial Automation

- Medical Equipment

#### Rev1 0

TREV I.U

Copyright@2018 Cosine Nanoelectronics Inc. All rights reserved

The information provided here is believed to be accurate and reliable. Cosine Nanoelectronics assumes no reliability for inaccuracies and omissions. Specifications described and contained here are subjected to change without notice on the purpose of improving the design and performance. All of this information described herein should not be implied or granted for any third party.

# **General Description**

The COS6505A/B/C Family are low-EMI push-pull transformer drivers, specifically designed for small form factor, isolated power supplies in isolated interface applications. The device drives a low-profile, center-tapped transformer primary from a 2.25-V to 5-V DC power supply. The secondary can be wound to provide any isolated voltage based on transformer turns ratio.

The COS6505AB/C consist of an oscillator followed by a gate drive circuit that provides the complementary output signals to drive the ground referenced N-channel power switches. The internal logic ensures break-before-make action between the two switches. The internal protection features under-voltage lockout, thermal shutdown and output current limiting. Low noise and low-EMI are achieved by slew rate control of the output switch voltage and through Spread Spectrum Clocking (SSC).

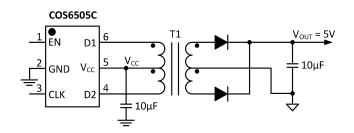

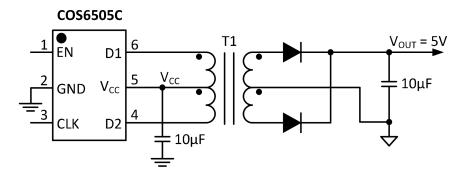

Simplified Schematic

# 1. Pin Configuration and Functions

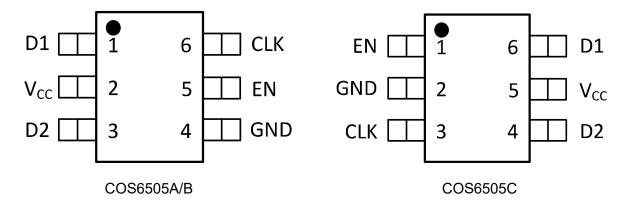

Figure 1 Pin Diagram

# Pin Description

|                | PIN          |      |      |                                                                                                                                                                                             |

|----------------|--------------|------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| COS6505<br>A/B | COS6505<br>C | Name | Туре | Description                                                                                                                                                                                 |

| 1              | 6            | D1   | 0    | Open drain output 1. Connect this pin to one end of the transformer primary side.                                                                                                           |

| 2              | 5            | Vcc  | Р    | Supply voltage input. Connect this pin to the center-tap of the transformer primary side. Buffer this voltage with a $1\mu F$ to $10\mu F$ ceramic capacitor.                               |

| 3              | 4            | D2   | 0    | Open drain output 2. Connect this pin to one end of the transformer primary side.                                                                                                           |

| 4              | 2            | GND  | Р    | Device ground. Connect this pin to the board ground                                                                                                                                         |

| 5              | 1            | EN   | I    | The EN pin turns the device on or off. Enable pin has an internal pull down resistor which keeps device disabled when not driven.                                                           |

| 6              | 3            | CLK  | I    | This pin is used to run the device with external clock. Internally it is pulled down to GND. If valid clock is not detected on this pin, the device shifts automatically to internal clock. |

# 2. Packaging and Ordering Information

| Model     | Package | Order Number | Package Option      | Marking<br>Information |

|-----------|---------|--------------|---------------------|------------------------|

| COSN6505A | SOT23-6 | COSN6505A    | Tape and Reel, 3000 | C6505A                 |

| COS6505B  | SOT23-6 | COSN6505B    | Tape and Reel, 3000 | C6505B                 |

| COSN6505C | SOT23-6 | COSN6505C    | Tape and Reel, 3000 | C6505C                 |

# 3. Product Specification

# 3.1 Absolute Maximum Ratings (1)

| Parameter                                                         | Min  | Max                  | Unit |

|-------------------------------------------------------------------|------|----------------------|------|

| DC supply voltage, V <sub>CC</sub>                                | -0.3 | 6                    | V    |

| Output switch voltage, V <sub>D1</sub> , V <sub>D2</sub>          |      | 18                   | V    |

| EN, CLK Voltage                                                   | -0.3 | V <sub>CC</sub> +0.5 | V    |

| Peak output switch current, I <sub>D1Pk</sub> , I <sub>D2Pk</sub> |      | 1.7                  | А    |

| Operating junction temperature                                    | -55  | +150                 | °C   |

| Storage temperature                                               | -65  | +150                 | °C   |

<sup>(1)</sup> Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

## 3.2 ESD Ratings

|                                           | Rating                            | Unit  |   |

|-------------------------------------------|-----------------------------------|-------|---|

|                                           | Human body mode (HBM), D1, D2     | ±8000 |   |

| Electrostatic Discharge, V <sub>ESD</sub> | Human body mode (HBM), other pins | ±2000 | V |

|                                           | Charge device model (CDM)         | ±1000 |   |

## 3.3 Thermal Data

| Parameter                                  | Rating        | Unit |

|--------------------------------------------|---------------|------|

| Package Thermal Resistance,R <sub>JA</sub> | 190 (SOT23-6) | °C/W |

# 3.4 Recommended Operating Conditions

| Parameter                          |                      |     | Тур. | Max. | Uni<br>t |

|------------------------------------|----------------------|-----|------|------|----------|

| DC Supply voltage, V <sub>CC</sub> |                      | 2.5 |      | 5.5  | V        |

| D1 and D2 output switch current    | 2.25 V < VCC < 2.8 V |     |      | 0.75 |          |

| - Primary-side                     | 2.8 V < VCC < 5.5 V  |     |      | 1    | Α        |

| Operating ambient temperature      |                      | -40 |      | +125 | °C       |

# 3.5 Electrical Characteristics

(V<sub>CC</sub>=5V, R<sub>L</sub>=  $50\Omega$  to V<sub>CC</sub>, T<sub>A</sub>=+ $25^{\circ}$ C, unless otherwise noted)

| Parameter                           | Symbol               | Conditions              | Min. | Тур. | Max. | Unit |

|-------------------------------------|----------------------|-------------------------|------|------|------|------|

| Voltage Supply                      |                      |                         |      |      |      |      |

| Average Supply Current              | Icc                  | EN=V <sub>CC</sub>      |      | 0.7  | 1.0  | mA   |

| V <sub>CC</sub> Current for EN=0    | I <sub>DIS</sub>     | EN=0                    |      | 0.1  |      | μA   |

| Leakage Current on D1, D2 for EN=0  | I <sub>LKG_D</sub>   | EN=0                    |      | 0.1  |      | μA   |

| Leakage Current on EN, CLK pin      | I <sub>LKG_IH</sub>  | EN, CLK=V <sub>CC</sub> |      | 10   | 20   | μA   |

| EN, CLK Pin Logic High<br>Threshold | V <sub>IN(ON)</sub>  |                         |      | 1.8  |      | ٧    |

| EN, CLK Pin Logic Low<br>Threshold  | V <sub>IN(OFF)</sub> |                         |      | 0.8  |      | V    |

| EN, CLK Pin Threshold<br>Hysteresis | H <sub>IN</sub>      |                         |      | 1    |      | ٧    |

| Positive-going UVLO threshold       | UVLO+                |                         |      | 2.25 |      | ٧    |

| Positive-going UVLO threshold       | UVLO-                |                         |      | 1.7  |      | ٧    |

| UVLO Threshold Hysteresis           | H <sub>uvlo</sub>    |                         |      | 0.5  |      | ٧    |

| CLK                                                                               |                  |                                                                   |     |      |      |        |  |

|-----------------------------------------------------------------------------------|------------------|-------------------------------------------------------------------|-----|------|------|--------|--|

|                                                                                   | fsw              | COS6505A                                                          | 130 | 160  | 200  | kHz    |  |

| D1, D2 Switching Frequency                                                        |                  | COS6505B/C                                                        | 360 | 420  | 520  |        |  |

| External Clock Frequency                                                          | f <sub>EXT</sub> | COS6505A                                                          | 100 |      | 600  | kHz    |  |

| External Clock Frequency                                                          | f <sub>EXT</sub> | COS6505B/C                                                        | 100 |      | 1600 | kHz    |  |

| Device Switches to Internal<br>Clock Delay (in case of invalid<br>external clock) | t <sub>D</sub>   |                                                                   | 7   |      | 15   | μs     |  |

| Output Stage                                                                      |                  |                                                                   |     |      |      |        |  |

|                                                                                   |                  | V <sub>CC</sub> = 4.5V, I <sub>D1</sub> ,I <sub>D2</sub> = 1 A    |     | 0.16 |      |        |  |

| Switch-on Resistance                                                              | Ron              | V <sub>CC</sub> = 2.8V, I <sub>D1</sub> ,I <sub>D2</sub> = 1 A    |     | 0.19 |      | Ω      |  |

|                                                                                   |                  | V <sub>CC</sub> = 2.25V, I <sub>D1</sub> ,I <sub>D2</sub> = 0.5 A |     | 0.21 |      |        |  |

| Average ON time mismatch between D1 and D2                                        | DMM              | R <sub>L</sub> = 50Ω                                              |     | 0%   |      |        |  |

| Voltage Slew Rate                                                                 | V <sub>SR</sub>  | COS6505A;<br>R <sub>L</sub> = $50\Omega$ to VCC                   |     | 50   |      | V/µs   |  |

| on D1 and D2                                                                      |                  | COS6505B/C;<br>R <sub>L</sub> = 50Ω to VCC                        |     | 150  |      |        |  |

| Current Slew Rate                                                                 | I <sub>SR</sub>  | COS6505A; $R_L = 5\Omega$ through transformer                     |     | 10   |      | - A/μs |  |

| on D1 and D2                                                                      |                  | COS6505A; $R_L = 5\Omega$ through transformer                     |     | 40   |      |        |  |

| O                                                                                 |                  | 2.25V < V <sub>CC</sub> < 2.8V                                    | 1.4 | 1.7  | 2.2  | A      |  |

| Current Clamp Limit                                                               | I <sub>LIM</sub> | 2.8V < V <sub>CC</sub> < 5.5V                                     | 0.6 | 1.2  | 1.9  |        |  |

| Dunals Dafara Malas Time                                                          |                  | COS6505A;<br>R <sub>L</sub> = $50\Omega$ to VCC                   |     | 115  |      |        |  |

| Break-Before-Make Time                                                            | tввм             | COS6505B/C;<br>R <sub>L</sub> = 50Ω to VCC                        |     | 85   |      | ns     |  |

| Thermal Shut Down                                                                 |                  |                                                                   |     |      |      |        |  |

| Shutdown Temperature                                                              | T <sub>SD</sub>  |                                                                   | 135 | 150  | 166  | °C     |  |

| Thermal Hysteresis                                                                | T <sub>HYS</sub> |                                                                   |     | 17   |      | °C     |  |

|                                                                                   | 1                | I                                                                 |     |      | L    |        |  |

# 4. Application Information

## 4.1 Overview

The COS6505A/B/C are low-EMI push-pull transformer drivers, specifically designed for small form factor, isolated power supplies in isolated interface applications. The devices drive a low-profile, center-tapped transformer primary from a 2.25-V to 5-V DC power supply. The secondary can be wound to provide any isolated voltage based on transformer turns ratio.

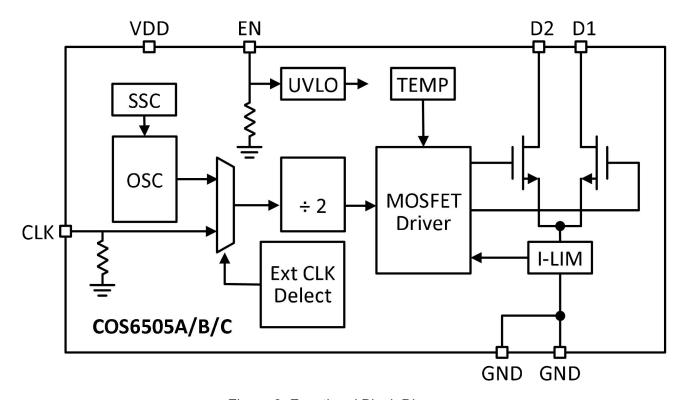

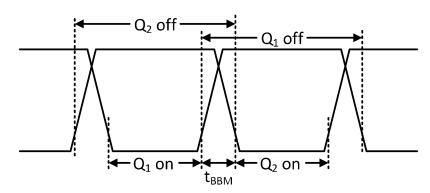

The COS6505A/B/C consist of an oscillator followed by a gate drive circuit that provides the complementary output signals to drive the ground referenced N-channel power switches (Figure 2). The internal logic ensures break-before-make action between the two switches (Figure 3). The internal protection features under-voltage lockout, thermal shutdown and output current limiting. Low noise and low-EMI are achieved by slew rate control of the output switch voltage and through Spread Spectrum Clocking (SSC).

## 4.2 Functional Block Diagram

Figure 2. Functional Block Diagram

Figure 3. Output Timing with Break-Before-Make Action

#### 4.3 Device Function Modes

#### 4.3.1 Enable Control

The device has a dedicated enable pin to put the device in very low power mode to save power when not in use. Enable pin has an internal pull down resistor which keeps device disabled when not driven. When disabled or when VCC is < 1.7 V, both drain outputs, D1 and D2, are tri-stated.

#### 4.3.2 External and Internal Clock Mode

The COS6505 has a CLK pin which can be used to synchronize the device with system clock and in turn with other COS6505 devices so that the system can control the exact switching frequency of the device. The Rising edge of the CLK is used to divide a clock by two and used to drive the gates. The device also has external clock fail safe feature which automatically switches the device to the internal clock if a valid input clock is not present for long. The built-in emissions reduction scheme of Spread Spectrum clocking is disabled when external clock is present.

#### 4.3.2 External and Internal Clock Mode

Radiated emissions is an important concern in high current switching power supplies. COS6505 addresses this by modulating its internal clock in such a way that the emitting energy is spread over multiple frequency bins. This Spread Spectrum clocking feature greatly improves the emissions performance of the entire power supply block and hence relieves the system designer from one major concern in isolated power supply design.

## 4.4 Typical Application Circuits

## 4.4.1 Unregulated Output versus Regulated Output

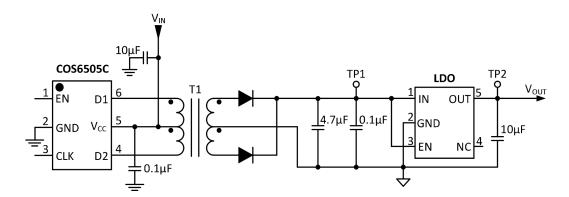

The output voltage of the unregulated converter (Figure 4) drops significantly over a wide range in load current. Therefore, in order to provide a stable, load independent supply while maintaining maximum possible efficiency, the implementation of a low dropout regulator (LDO) is strongly advised (Figure 5).

Figure 4. Unregulated Output for Low-Current Loads

Figure 5. Regulated Output for Stable Supplies and High Current Loads

## 4.4.2 Higher Output Voltage Designs

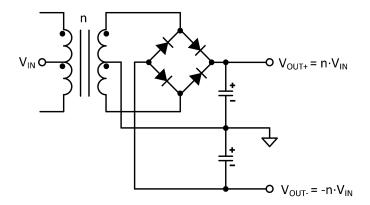

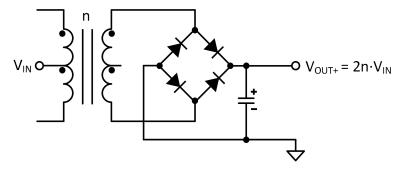

The device can drive push-pull converters that provide high output voltages of up to 30 V, or bipolar outputs of up to ±15 V. Using commercially available center-tapped transformers, with their rather low turns ratios of 0.8 to 5, requires different rectifier topologies to achieve high output voltages. Figure 6 and Figure 7 show some of these topologies together with their respective open-circuit output voltages.

Figure 6. Bridge Rectifier with Center-Tapped Secondary Enables Bipolar Outputs

Figure 7. Bridge Rectifier without Center-Tapped Secondary Performs Voltage Doubling

## 4.5 Component Selection

#### 4.5.1 Diode Selection

A rectifier diode should always possess low-forward voltage to provide as much voltage to the converter output as possible. When used in high-frequency switching applications, the diode must also possess a short recovery time. Schottky diodes meet both requirements and are therefore strongly recommended in push-pull converter designs.

#### 4.5.2 Capacitor Selection

The input bulk capacitor at the center-tap of the primary supports large currents into the primary during the fast switching transients. For minimum ripple make this capacitor 1µF to 10µF. In a 2-layer PCB design with a dedicated ground plane, place this capacitor close to the primary center-tap to minimize trace inductance.

The bulk capacitor at the rectifier output smooths the output voltage. Make this capacitor  $1\mu\text{F}$  to  $10\mu\text{F}$ . The small capacitor at the regulator input is not necessarily required. However, good analog design practice suggests, using a small value of 47 nF to 100 nF improves the regulator's transient response and noise rejection.

The LDO output capacitor buffers the regulated output for the subsequent isolator and transceiver circuitry. The choice of output capacitor depends on the LDO stability requirements specified in the data sheet. However, in most cases, a low-ESR ceramic capacitor in the range of 4.7  $\mu$ F to 10  $\mu$ F will satisfy these requirements.

#### 4.5.3 Transformer Selection

The factors that must be considered before making the transformer decision include: isolation voltage, transformer wattage, V-t product and turns ratio.

#### 4.5.3.1 V-t Product Calculation

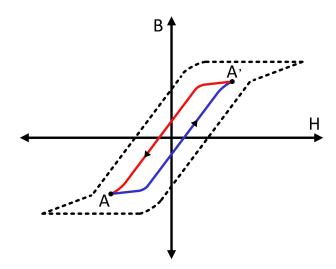

The volt-seconds (V-t) product is an important parameter as it determines the core magnetization during each switching cycle. If the V-t products of both phases are not identical, an imbalance in flux density swing results with an offset from the origin of the B-H curve (Figure 8). If balance is not restored, the offset increases with each following cycle and the transformer slowly creeps toward the saturation region.

Figure 8. An Ideal Magnetizing Curve for a Push-Pull Converter

To prevent a transformer from saturation its V-t product must be greater than the maximum V-t product applied by the device. The maximum voltage delivered by the device is the nominal converter input plus 10%. The maximum time this voltage is applied to the primary is half the period of the lowest frequency at the specified input voltage. Therefore, the transformer's minimum V-t product is determined through:

$$Vt_{min} \ge V_{IN-max} \times \frac{T_{max}}{2} = \frac{V_{IN-max}}{2 \times f_{min}}$$

(1)

Taking an example of fmin as 360kHz for COS6505B/C with a 5 V supply, Equation 1 yields the minimum V-t products of:

$$Vt_{min} \ge \frac{5.5V}{2 \times 360 \text{ kHz}} = 7.6 \text{ V}\mu\text{s}$$

(2)

#### 4.5.3.2 Turns Ratio Estimate

The minimum transformation ratio is expressed through the ratio of minimum secondary to minimum primary voltage multiplied by a correction factor that takes the transformer's typical efficiency of 97% into account:

$$N_{min} = 1.03 \times V_{S-min} / V_{P-min}$$

(3)

Then calculating the available minimum primary voltage,  $V_P$ -min, involves subtracting the maximum possible drain-source voltage of the device,  $V_{DS-max}$ , from the minimum converter input voltage  $V_{IN-min}$ :

$$V_{P-min} = V_{IN-min} - V_{DS-max}$$

$$= V_{IN-min} - R_{DS-max} \times I_{Dmax}$$

(4)

$V_{S-min}$  must be large enough to allow for a maximum voltage drop,  $V_{F-max}$ , across the rectifier diode and still provide sufficient input voltage for the regulator to remain in regulation.

$$V_{S-min} = V_{F-max} + V_{DO-max} + V_{O-max}$$

(5)

Inserting Equation 4 and Equation 5 into Equation 3 provides the minimum turns ration with:

$$n_{min} = 1.03 \times \frac{V_{F-man} + V_{DO-man} + V_{O-man}}{V_{IN-min} - R_{DS-man} \times I_{D-man}}$$

(6)

## 4.5.4 Power Supply Recommendations

The COS6505A/B/C are designed to operate from an input voltage supply range between 2.25 V and 5V nominal. This input supply must be regulated within  $\pm 10\%$ . If the input supply is located more than a few inches from the device, a 0.1  $\mu$ F by-pass capacitor should be connected as close as possible to the device VCC pin and a  $10\mu$ F capacitor should be connected close to the transformer center-tap pin.

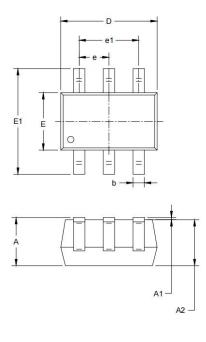

# 5. Package Information

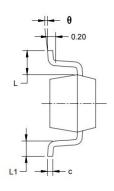

## **5.1 SOT23-6 (Package Outline Dimensions)**

| Symbol |          | nsions<br>imeters | Dimensions<br>In Inches |       |  |

|--------|----------|-------------------|-------------------------|-------|--|

|        | Min      | Max               | Min                     | Max   |  |

| Α      | 1.050    | 1.250             | 0.041                   | 0.049 |  |

| A1     | 0.000    | 0.100             | 0.000                   | 0.004 |  |

| A2     | 1.050    | 1.150             | 0.041                   | 0.045 |  |

| b      | 0.300    | 0.400             | 0.012                   | 0.016 |  |

| С      | 0.100    | 0.200             | 0.004                   | 0.008 |  |

| D      | 2.820    | 3.020             | 0.111                   | 0.119 |  |

| E      | 1.500    | 1.700             | 0.059                   | 0.067 |  |

| E1     | 2.650    | 2.950             | 0.104 0.116             |       |  |

| е      | 0.950TYP |                   | 0.037                   | 7TYP  |  |

| e1     | 1.800    | 2.000             | 0.071                   | 0.079 |  |

| L      | 0.700    | REF               | 0.028                   | BREF  |  |

| L1     | 0.300    | 0.600             | 0.012                   | 0.024 |  |

| θ      | 0°       | 8°                | 0°                      | 8°    |  |